# M58LR128HC M58LR128HD

128 Mbit (x16, Mux I/O, Multiple Bank, Multilevel interface, Burst)

#### **Features**

- Supply voltage

- V<sub>DD</sub> = 1.7 V to 2.0 V for program, erase and read

- V<sub>DDQ</sub> = 1.7 V to 2.0 V for I/O Buffers

- V<sub>PP</sub> = 9 V for fast program

- Multiplexed address/data

- Synchronous / Asynchronous Read

- Synchronous Burst Read mode: 66 MHz

- Random Access: 70 ns

- Synchronous Burst Read Suspend

- Programming time

- 2.5 µs typical Word program time using Buffer Enhanced Factory Program command

- Memory organization

- Multiple Bank memory array: 8 Mbit Banks

- Parameter Blocks (top or bottom location)

- Dual operations

- program/erase in one Bank while read in others

- No delay between read and write operations

- Block locking

- All blocks locked at power-up

- Any combination of blocks can be locked with zero latency

- WP for Block Lock-Down

- Absolute Write Protection with V<sub>PP</sub> = V<sub>SS</sub>

### 1.8 V supply Flash memories

- Security

- 64 bit unique device number

- 2112 bit user programmable OTP Cells

- Common Flash Interface (CFI)

- 100 000 program/erase cycles per block

- Electronic signature

- Manufacturer Code: 20h

- Top Device Codes: M58LR128HC: 882Eh

- Bottom Device Codes M58LR128HD: 882Fh

- VFBGA44 package

- ECOPACK® compliant

## **Contents**

| 1 | Desc | ription                                 | 8  |

|---|------|-----------------------------------------|----|

| 2 | Sign | al descriptions                         | 3  |

|   | 2.1  | Address Inputs (ADQ0-ADQ15 and A16-A22) | 3  |

|   | 2.2  | Data Input/Output (ADQ0-ADQ15)          | 3  |

|   | 2.3  | Chip Enable (E)                         | 3  |

|   | 2.4  | Output Enable (G) 1                     | 3  |

|   | 2.5  | Write Enable ( $\overline{W}$ )         | 3  |

|   | 2.6  | Write Protect (WP)                      | 3  |

|   | 2.7  | Reset (RP)                              | 4  |

|   | 2.8  | Latch Enable ( $\overline{L}$ )         | 4  |

|   | 2.9  | Clock (K)                               | 4  |

|   | 2.10 | Wait (WAIT)                             | 4  |

|   | 2.11 | V <sub>DD</sub> supply voltage          | 4  |

|   | 2.12 | V <sub>DDQ</sub> supply voltage         | 4  |

|   | 2.13 | V <sub>PP</sub> Program supply voltage  | 5  |

|   | 2.14 | V <sub>SS</sub> ground                  | 5  |

|   | 2.15 | V <sub>SSQ</sub> ground                 | 5  |

| 3 | Bus  | operations1                             | 6  |

|   | 3.1  | Bus Read 1                              | 6  |

|   | 3.2  | Bus Write 1                             | 6  |

|   | 3.3  | Address Latch 1                         | 6  |

|   | 3.4  | Output Disable                          | 6  |

|   | 3.5  | Standby 1                               | 7  |

|   | 3.6  | Reset 1                                 | 7  |

| 4 | Com  | mand interface                          | 8  |

|   | 4.1  | Read Array command1                     | 9  |

|   | 4.2  | Read Status Register command1           | 9  |

|   | 4.3  | Read Electronic Signature command       | 20 |

|   | 4.4  | Read CFI Query command2                 | 20 |

|   |      |                                         |    |

|   | 4.5   | Clear Status Register command                     |

|---|-------|---------------------------------------------------|

|   | 4.6   | Block Erase command 2                             |

|   | 4.7   | The Blank Check command                           |

|   | 4.8   | Program command                                   |

|   | 4.9   | Buffer Program command                            |

|   | 4.10  | Buffer Enhanced Factory Program command           |

|   |       | 4.10.1 Setup Phase                                |

|   |       | 4.10.2 Program and Verify Phase                   |

|   |       | 4.10.3 Exit Phase                                 |

|   | 4.11  | Program/Erase Suspend command                     |

|   | 4.12  | Program/Erase Resume command                      |

|   | 4.13  | Protection Register Program command               |

|   | 4.14  | Set Configuration Register command                |

|   | 4.15  | Block Lock command                                |

|   | 4.16  | Block Unlock command                              |

|   | 4.17  | Block Lock-Down command                           |

| 5 | Statu | s Register                                        |

|   | 5.1   | Program/Erase Controller status bit (SR7)         |

|   | 5.2   | Erase Suspend status bit (SR6)                    |

|   | 5.3   | Erase/Blank Check status bit (SR5)                |

|   | 5.4   | Program status bit (SR4) 36                       |

|   | 5.5   | V <sub>PP</sub> status bit (SR3)                  |

|   | 5.6   | Program Suspend status bit (SR2)                  |

|   | 5.7   | Block Protection status bit (SR1) 3               |

|   | 5.8   | Bank Write/Multiple Word Program status bit (SR0) |

| 6 | Confi | guration Register                                 |

|   | 6.1   | Read Select bit (CR15)                            |

|   | 6.2   | X-Latency bits (CR13-CR11)                        |

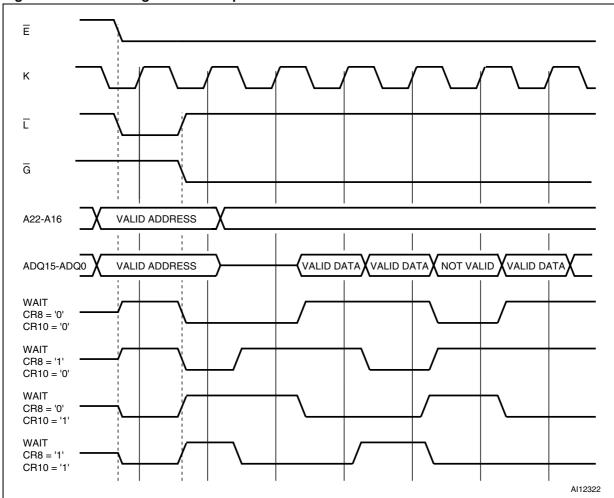

|   | 6.3   | Wait Polarity bit (CR10)                          |

|   | 6.4   | Data Output Configuration bit (CR9)               |

|   | 6.5   | Wait Configuration bit (CR8)                      |

|   | 6.6   | Burst type bit (CR7)                              |

|   |       |                                                   |

|          | 6.7        | Valid Clock edge bit (CR6)                  | 41 |

|----------|------------|---------------------------------------------|----|

|          | 6.8        | Wrap burst bit (CR3)                        | 41 |

|          | 6.9        | Burst length bits (CR2-CR0)                 | 41 |

|          |            |                                             |    |

| 7        | Rea        | d modes                                     | 47 |

|          | 7.1        | Asynchronous Read mode                      | 47 |

|          | 7.2        | Synchronous Burst Read mode                 | 47 |

|          |            | 7.2.1 Synchronous Burst Read Suspend        | 48 |

|          | 7.3        | Single Synchronous Read mode                | 48 |

| 8        | Dua        | I operations and Multiple Bank architecture | 49 |

| 9        | Bloc       | ck locking                                  | 51 |

|          | 9.1        | Reading a Block's lock status               | 51 |

|          | 9.2        | Locked state                                | 51 |

|          | 9.3        | Unlocked state                              | 51 |

|          | 9.4        | Lock-Down state                             | 52 |

|          | 9.5        | Locking operations during Erase Suspend     | 52 |

| 10       | Prog       | gram and erase times and endurance cycles   | 54 |

| 11       | Max        | imum rating                                 | 56 |

| 12       | DC a       | and AC parameters                           | 57 |

| 13       | Pacl       | kage mechanical                             | 72 |

| 14       | Part       | numbering                                   | 76 |

| Appendix | ( <b>A</b> | Block address tables                        | 77 |

| Appendix | (В (       | Common Flash Interface                      | 85 |

| Appendix | C I        | Flowcharts and pseudo codes                 | 95 |

| Appendix | (D (       | Command interface state tables              | 04 |

| M58LR128HC, M58LR128HD | Contents |

|------------------------|----------|

| Revision history       | 113      |

Numonyx 5/114

# List of tables

| Table 1.  | Signal names                                                             | 10  |

|-----------|--------------------------------------------------------------------------|-----|

| Table 2.  | M58LR128HC/D bank architecture                                           | 12  |

| Table 3.  | Bus operations                                                           | 17  |

| Table 4.  | Command codes                                                            | 18  |

| Table 5.  | Standard commands                                                        | 31  |

| Table 6.  | Factory Commands                                                         | 32  |

| Table 7.  | Electronic signature codes                                               | 32  |

| Table 8.  | Protection Register locks                                                | 34  |

| Table 9.  | Status Register bits                                                     | 38  |

| Table 10. | X-latency settings                                                       | 39  |

| Table 11. | Configuration Register                                                   | 42  |

| Table 12. | Burst type definition                                                    | 43  |

| Table 13. | Dual operations allowed in other banks                                   | 49  |

| Table 14. | Dual operations allowed in same bank                                     | 50  |

| Table 15. | Dual operation limitations                                               | 50  |

| Table 16. | Lock status                                                              | 53  |

| Table 17. | Program/Erase times and endurance cycles                                 | 54  |

| Table 18. | Absolute maximum ratings                                                 | 56  |

| Table 19. | Operating and AC measurement conditions                                  | 57  |

| Table 20. | Capacitance                                                              | 58  |

| Table 21. | DC characteristics - currents                                            | 59  |

| Table 22. | DC characteristics - voltages                                            | 60  |

| Table 23. | Asynchronous Read AC characteristics                                     | 62  |

| Table 24. | Synchronous Read AC characteristics                                      | 66  |

| Table 25. | Write AC characteristics, Write Enable controlled                        | 68  |

| Table 26. | Write AC characteristics, Chip Enable controlled                         |     |

| Table 27. | Reset and Power-up AC characteristics                                    | 71  |

| Table 28. | VFBGA44 7.7x9mm - 10x4 ball array, 0.50mm pitch, package mechanical data | 73  |

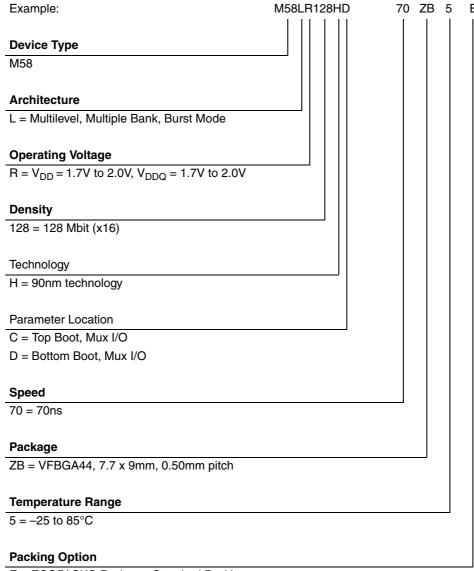

| Table 29. | Ordering information scheme                                              |     |

| Table 30. | Top boot block addresses, M58LR128HC                                     | 77  |

| Table 31. | Bottom boot block addresses, M58LR128HD                                  | 81  |

| Table 32. | Query structure overview                                                 | 85  |

| Table 33. | CFI query identification string                                          | 86  |

| Table 34. | CFI query system interface information                                   |     |

| Table 35. | Device geometry definition                                               | 88  |

| Table 36. | Primary Algorithm-Specific Extended Query Table                          |     |

| Table 37. | Protection Register information                                          |     |

| Table 38. | Burst Read information                                                   | 90  |

| Table 39. | Bank and Erase Block region information                                  | 91  |

| Table 40. | Bank and Erase Block region 1 information                                | 91  |

| Table 41. | Bank and Erase Block region 2 information                                | 93  |

| Table 42. | Command Interface states - modify table, next state                      |     |

| Table 43. | Command Interface states - modify table, next output state               |     |

| Table 44. | Command interface states - lock table, next state                        |     |

| Table 45. | Command interface states - lock table, next output state                 |     |

| Table 46. | Document revision history                                                | 113 |

# **List of figures**

| Figure 1.  | Logic diagram                                                                | 10    |

|------------|------------------------------------------------------------------------------|-------|

| Figure 2.  | VFBGA connections (top view through package)                                 | 11    |

| Figure 3.  | M58LR128HC/D memory map                                                      | 12    |

| Figure 4.  | Protection Register memory map                                               | 33    |

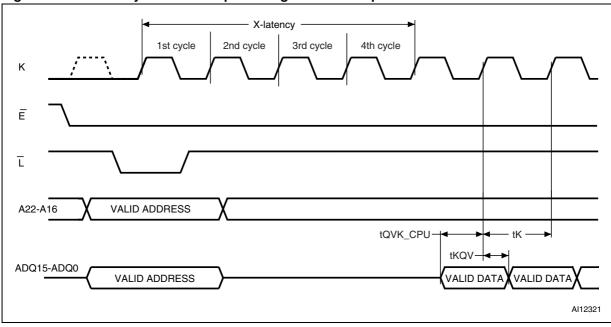

| Figure 5.  | X-Latency and data output configuration example                              | 45    |

| Figure 6.  | Wait configuration example                                                   | 46    |

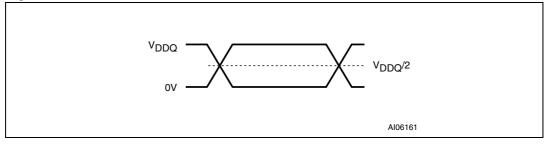

| Figure 7.  | AC measurement I/O waveform                                                  | 57    |

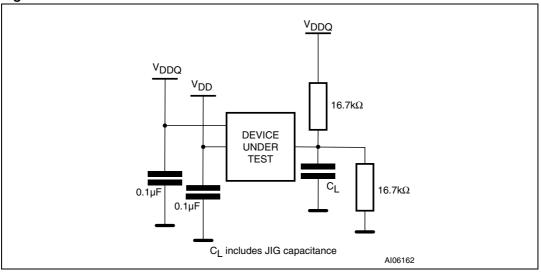

| Figure 8.  | AC measurement load circuit                                                  | 58    |

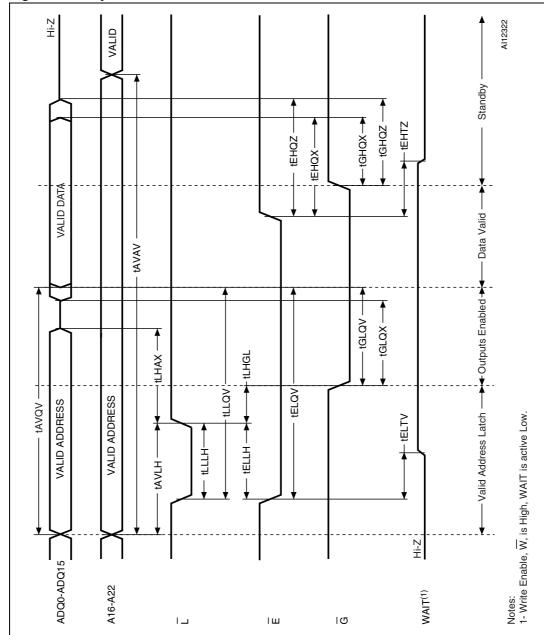

| Figure 9.  | asynchronous random access Read AC waveforms                                 | 61    |

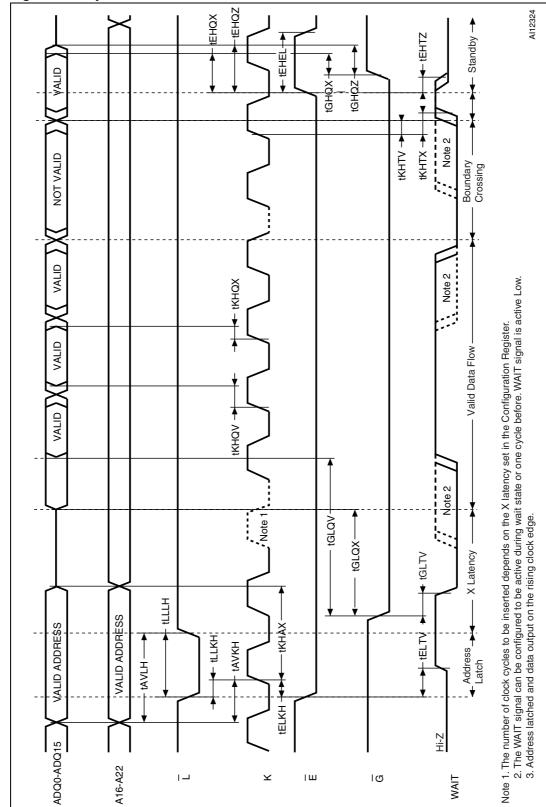

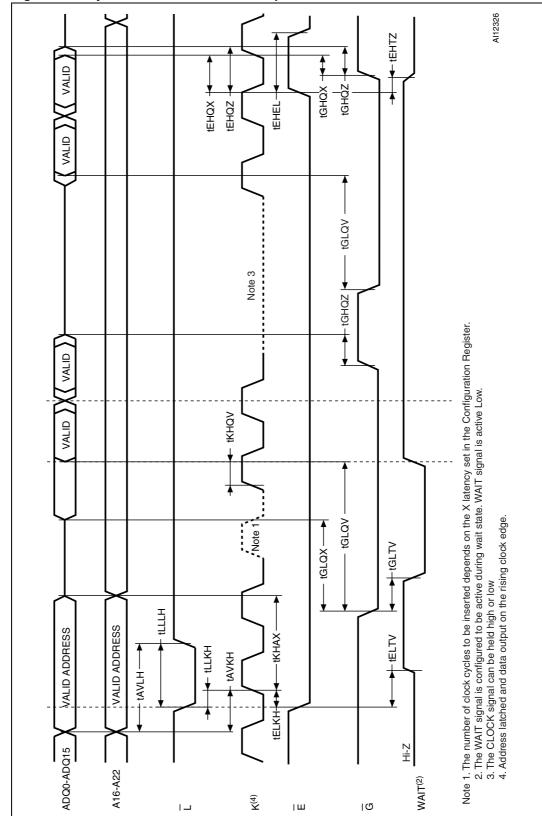

| Figure 10. | Synchronous Burst Read AC waveforms                                          | 63    |

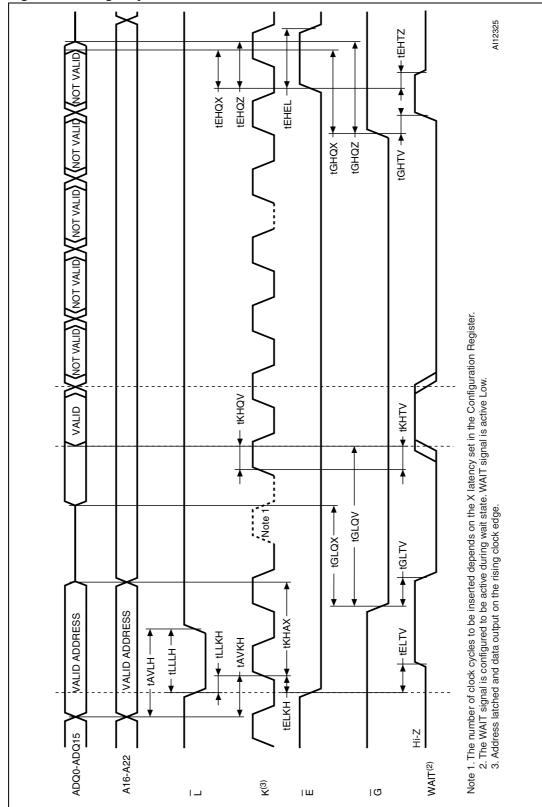

| Figure 11. | Single Synchronous Read AC waveforms                                         | 64    |

| Figure 12. | Synchronous Burst Read Suspend AC waveforms                                  | 65    |

| Figure 13. | Clock input AC waveform                                                      | 66    |

| Figure 14. | Write AC waveforms, Write Enable controlled                                  | 67    |

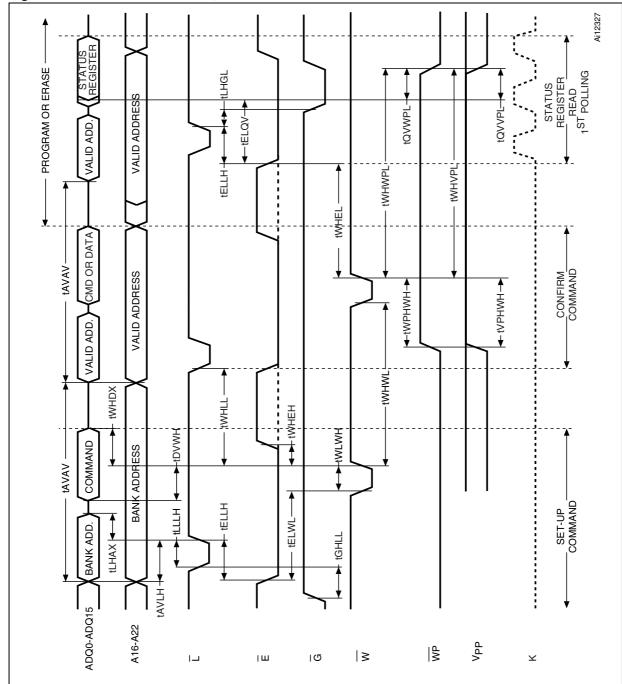

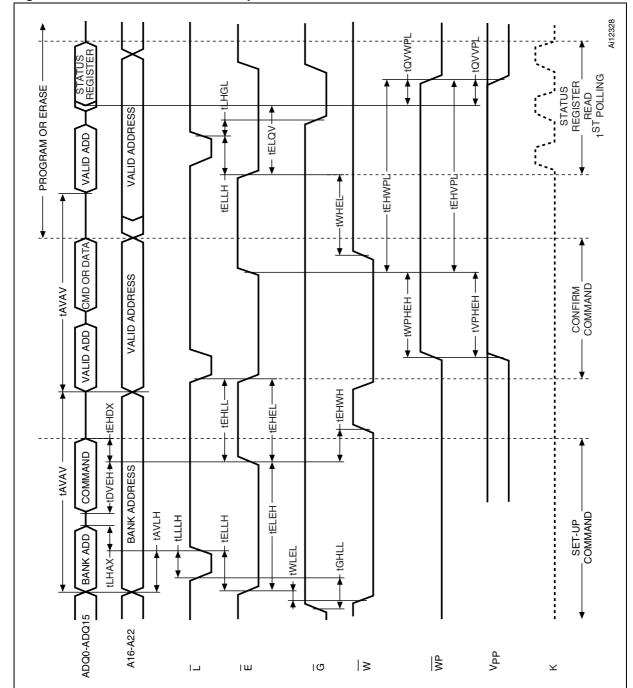

| Figure 15. | Write AC waveforms, Chip Enable controlled                                   | 69    |

| Figure 16. | Reset and Power-up AC waveforms                                              | 71    |

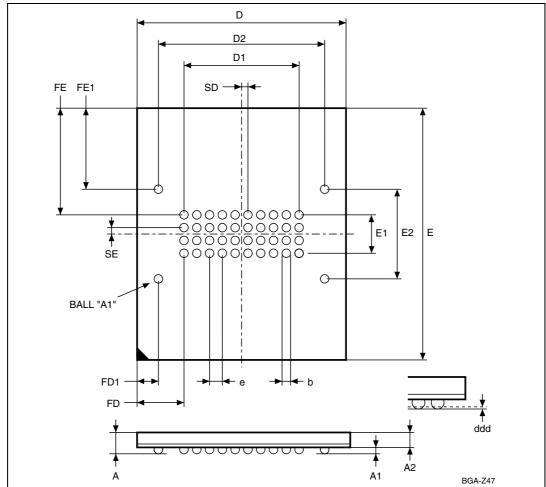

| Figure 17. | VFBGA44 7.7x9mm - 10x4 ball array, 0.50mm pitch, Bottom View Package Outline | 72    |

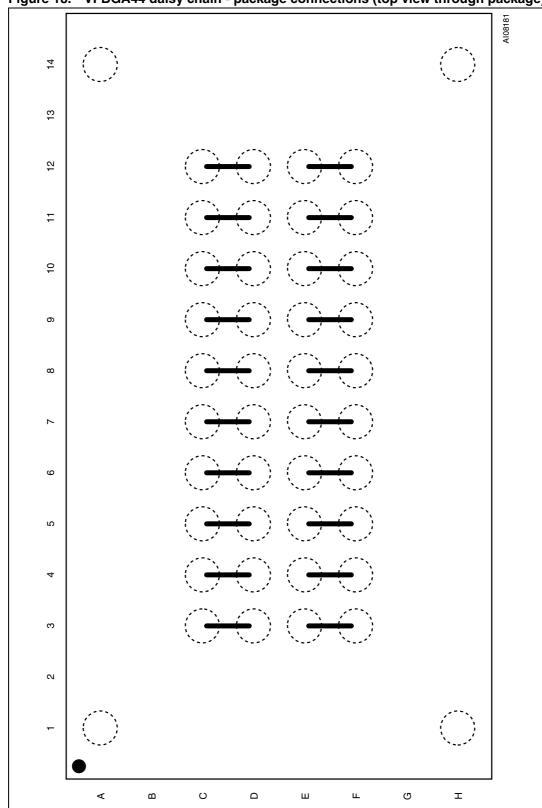

| Figure 18. | VFBGA44 daisy chain - package connections (top view through package)         | 74    |

| Figure 19. | VFBGA44 daisy chain - PCB connection proposal (top view through package)     | 75    |

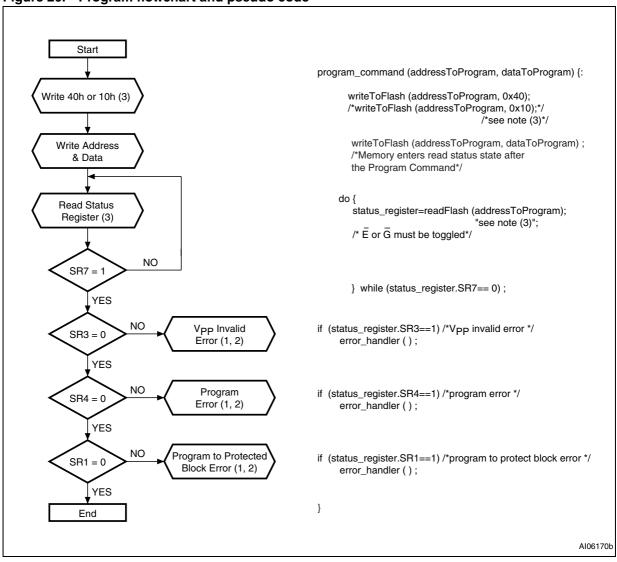

| Figure 20. | Program flowchart and pseudo code                                            | 95    |

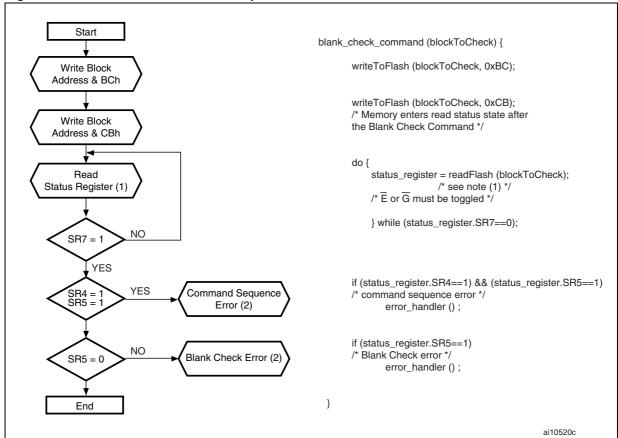

| Figure 21. | Blank Check flowchart and pseudo code                                        | 96    |

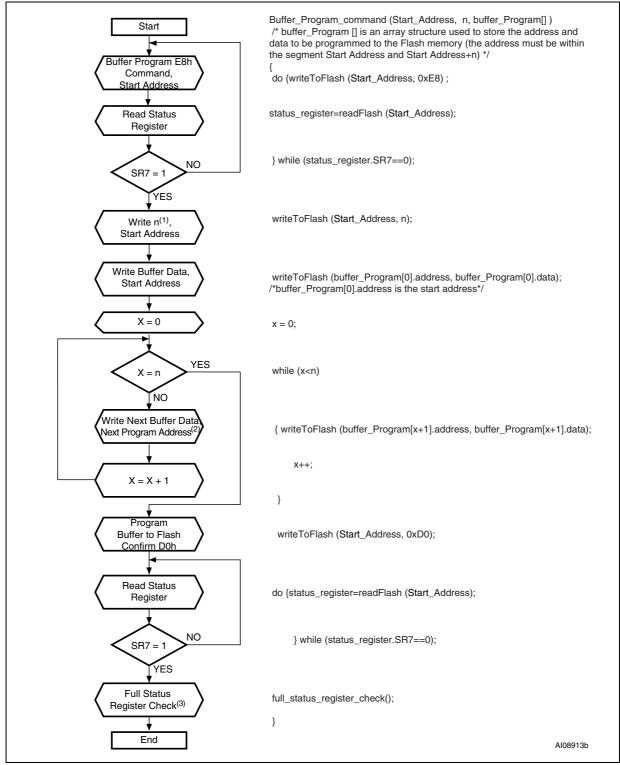

| Figure 22. | Buffer Program flowchart and pseudo code                                     | 97    |

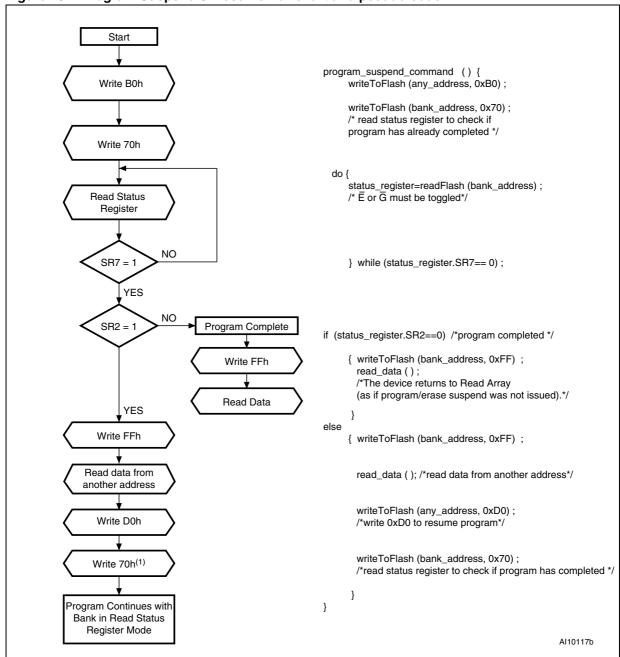

| Figure 23. | Program Suspend & Resume flowchart and pseudo code                           | 98    |

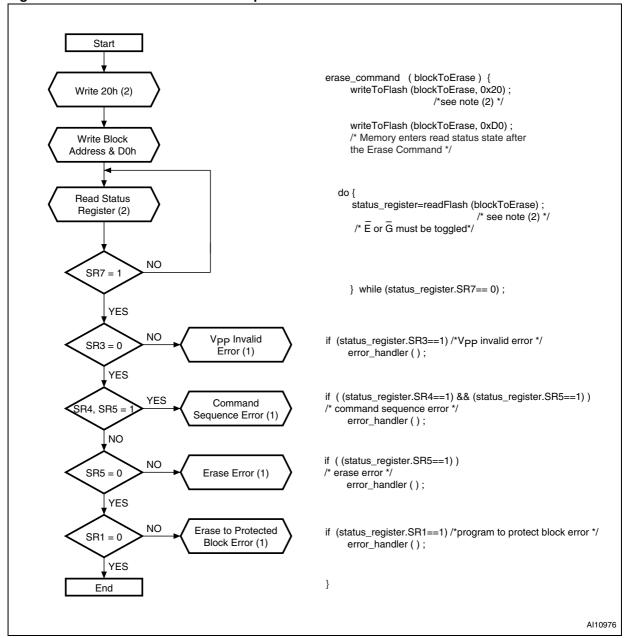

| Figure 24. | Block Erase flowchart and pseudo code                                        | 99    |

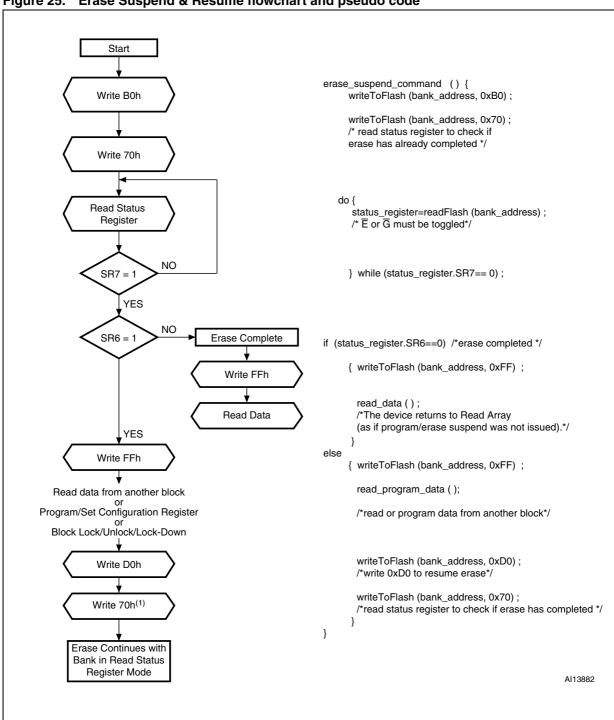

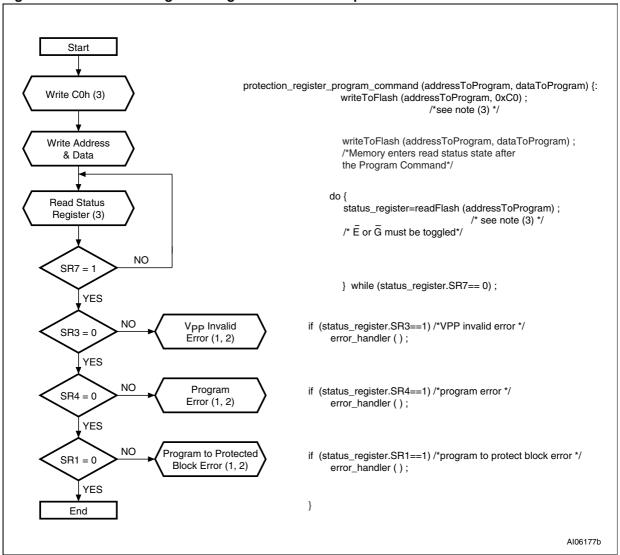

| Figure 25. | Erase Suspend & Resume flowchart and pseudo code                             | . 100 |

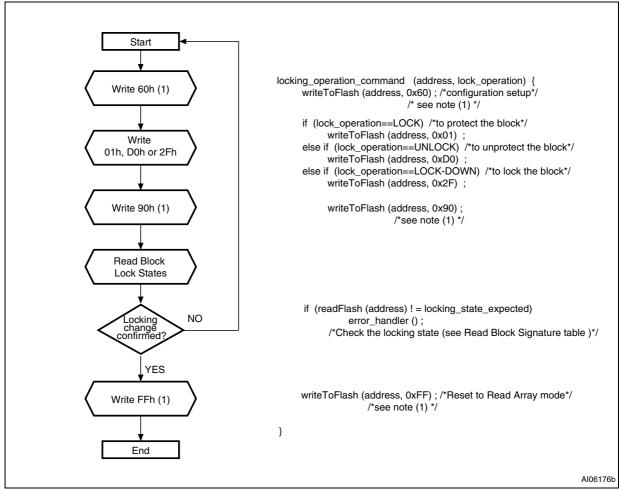

| Figure 26. | Locking operations flowchart and pseudo code                                 |       |

| Figure 27. | Protection Register Program flowchart and pseudo code                        | . 102 |

| Figure 28. | Buffer Enhanced Factory Program flowchart and pseudo code                    | . 103 |

### 1 Description

The M58LR128HC/D are 128 Mbit (8 Mbit  $\times$ 16) non-volatile Flash memories. They may be erased electrically at block level and programmed in-system on a Word-by-Word basis using a 1.7 V to 2.0 V V<sub>DD</sub> supply for the circuitry and a 1.7 V to 2.0 V V<sub>DDQ</sub> supply for the Input/Output pins. An optional 9 V V<sub>PP</sub> power supply is provided to speed up factory programming.

The first sixteen address lines are multiplexed with the Data Input/Output signals on the multiplexed address/data bus ADQ0-ADQ15. The remaining address lines A16-A22 are the Most Significant Bit addresses.

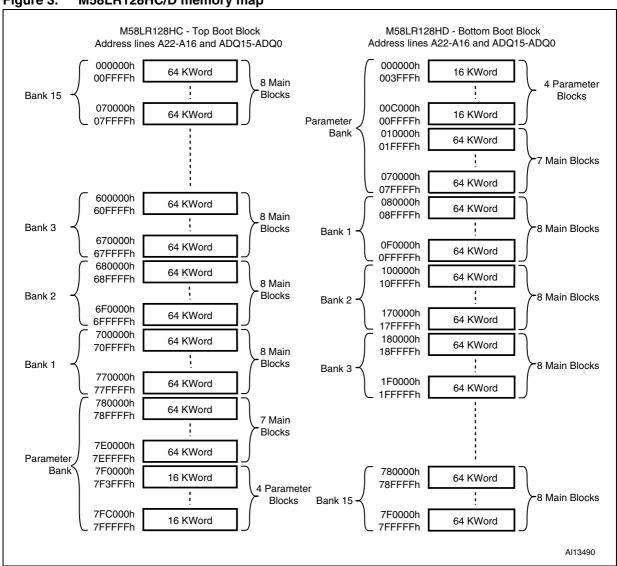

The devices feature an asymmetrical block architecture. The M58LR128HC/D have an array of 131 blocks, and are divided into 8 Mbit banks. There are 15 banks each containing 8 main blocks of 64 KWords, and one parameter bank containing 4 parameter blocks of 16 KWords and 7 main blocks of 64 KWords.

The Multiple Bank Architecture allows Dual Operations, while programming or erasing in one bank, read operations are possible in other banks. Only one bank at a time is allowed to be in program or erase mode. It is possible to perform burst reads that cross bank boundaries. The bank architecture is summarized in *Table 2*, and the memory map is shown in *Figure 3*. The Parameter Blocks are located at the top of the memory address space for the M58LR128HC, and at the bottom for the M58LR128HD.

Each block can be erased separately. Erase can be suspended, in order to perform a program or read operation in any other block, and then resumed. Program can be suspended to read data at any memory location except for the one being programmed, and then resumed. Each block can be programmed and erased over 100 000 cycles using the supply voltage  $V_{DD}$ . There is a Buffer Enhanced Factory programming command available to speed up programming.

Program and erase commands are written to the Command Interface of the memory. An internal Program/Erase Controller takes care of the timings necessary for program and erase operations. The end of a program or erase operation can be detected and any error conditions identified in the Status Register. The command set required to control the memory is consistent with JEDEC standards.

The device supports Synchronous Burst Read and Asynchronous Read from all blocks of the memory array; at power-up the device is configured for Asynchronous Read. In Synchronous Burst Read mode, data is output on each clock cycle at frequencies of up to 66 MHz. The Synchronous Burst Read operation can be suspended and resumed.

The device features an Automatic Standby mode. When the bus is inactive during Asynchronous Read operations, the device automatically switches to the Automatic Standby mode. In this condition the power consumption is reduced to the standby value and the outputs are still driven.

The M58LR128HC/D features an instant, individual block locking scheme that allows any block to be locked or unlocked with no latency, enabling instant code and data protection. All blocks have three levels of protection. They can be locked and locked-down individually preventing any accidental programming or erasure. There is an additional hardware protection against program and erase. When  $V_{PP} \le V_{PPLK}$  all blocks are protected against program or erase. All blocks are locked at power-up.

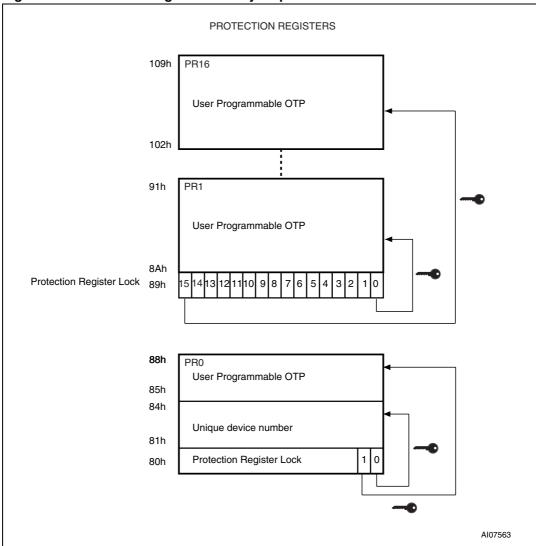

The device includes 17 Protection Registers and 2 Protection Register locks, one for the first Protection Register and the other for the 16 One-Time-Programmable (OTP) Protection Registers of 128 bits each. The first Protection Register is divided into two segments: a 64 bit segment containing a unique device number written by Numonyx, and a 64 bit segment One-Time-Programmable (OTP) by the user. The user programmable segment can be permanently protected. *Figure 4*, shows the Protection Register Memory Map.

The M58LR128HC/D are offered in a VFBGA44, 7.7 x 9 mm, 0.50 mm pitch package. They are supplied with all the bits erased (set to '1').

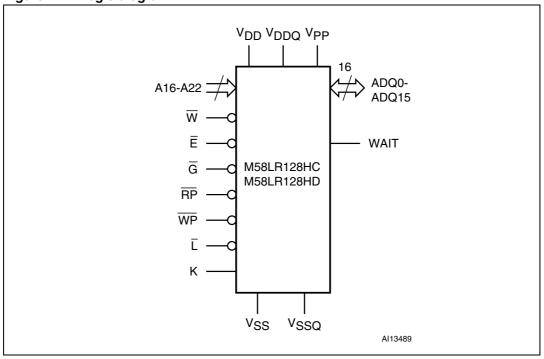

Figure 1. Logic diagram

Table 1. Signal names

| - u.u u.g        |                                                      |

|------------------|------------------------------------------------------|

| A16-A22          | Address Inputs                                       |

| ADQ0-ADQ15       | Data Input/Outputs or Address Inputs, Command Inputs |

| Ē                | Chip Enable                                          |

| G                | Output Enable                                        |

| W                | Write Enable                                         |

| RP               | Reset                                                |

| WP               | Write Protect                                        |

| К                | Clock                                                |

| Ī                | Latch Enable                                         |

| WAIT             | Wait                                                 |

| $V_{DD}$         | Supply Voltage                                       |

| $V_{DDQ}$        | Supply Voltage for Input/Output Buffers              |

| V <sub>PP</sub>  | Optional Supply Voltage for Fast Program & Erase     |

| V <sub>SS</sub>  | Ground                                               |

| V <sub>SSQ</sub> | Ground Input/Output Supply                           |

| NC               | Not Connected Internally                             |

| DU               | Do Not Use                                           |

| L                |                                                      |

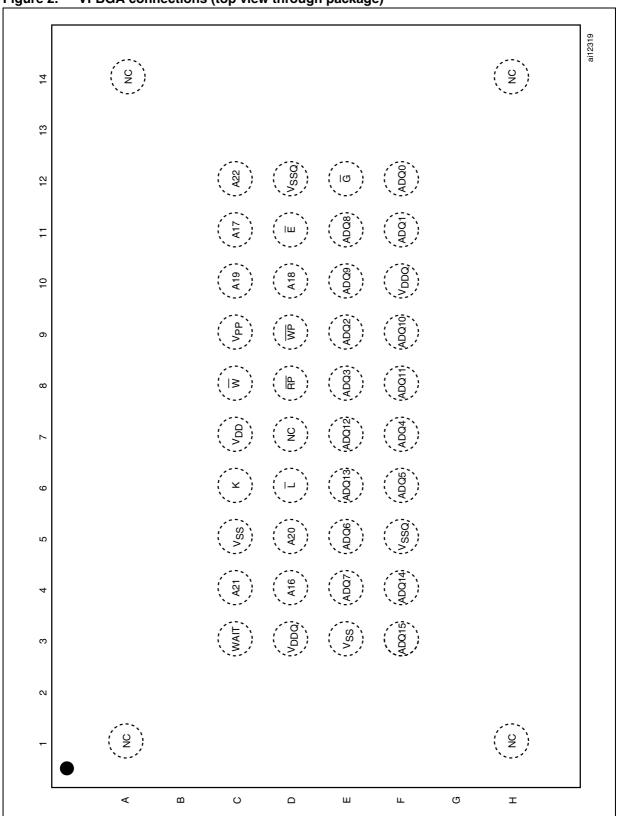

Figure 2. VFBGA connections (top view through package)

Numonyx 11/114

Table 2. M58LR128HC/D bank architecture

| Number         | Bank Size | Parameter Blocks      | Main Blocks           |

|----------------|-----------|-----------------------|-----------------------|

| Parameter Bank | 8 Mbits   | 4 blocks of 16 KWords | 7 blocks of 64 KWords |

| Bank 1         | 8 Mbits   | -                     | 8 blocks of 64 KWords |

| Bank 2         | 8 Mbits   | -                     | 8 blocks of 64 KWords |

| Bank 3         | 8 Mbits   | -                     | 8 blocks of 64 KWords |

| l              |           |                       |                       |

| Bank 14        | 8 Mbits   | -                     | 8 blocks of 64 KWords |

| Bank 15        | 8 Mbits   | -                     | 8 blocks of 64 KWords |

Figure 3. M58LR128HC/D memory map

### 2 Signal descriptions

See Figure 1: Logic diagram and Table 1: Signal names, for a brief overview of the signals connected to this device.

#### 2.1 Address Inputs (ADQ0-ADQ15 and A16-A22)

The Address Inputs select the cells in the memory array to access during Bus Read operations. During Bus Write operations they control the commands sent to the Command Interface of the Program/Erase Controller.

#### 2.2 Data Input/Output (ADQ0-ADQ15)

The Data I/O output the data stored at the selected address during a Bus Read operation or input a command or the data to be programmed during a Bus Write operation.

### 2.3 Chip Enable $(\overline{E})$

The Chip Enable input activates the memory control logic, input buffers, decoders and sense amplifiers. When Chip Enable is at  $V_{IL}$  and Reset is at  $V_{IH}$  the device is in active mode. When Chip Enable is at  $V_{IH}$  the memory is deselected, the outputs are high impedance and the power consumption is reduced to the standby level.

### 2.4 Output Enable ( $\overline{G}$ )

The Output Enable input controls data outputs during the Bus Read operation of the memory.

### 2.5 Write Enable $(\overline{W})$

The Write Enable input controls the Bus Write operation of the memory's Command Interface. The data and address inputs are latched on the rising edge of Chip Enable or Write Enable whichever occurs first.

### 2.6 Write Protect (WP)

Write Protect is an input that gives an additional hardware protection for each block. When Write Protect is at  $V_{IL}$ , the Lock-Down is enabled and the protection status of the Locked-Down blocks cannot be changed. When Write Protect is at  $V_{IH}$ , the Lock-Down is disabled and the Locked-Down blocks can be locked or unlocked. (refer to *Table 16: Lock status*).

### 2.7 Reset (RP)

The Reset input provides a hardware reset of the memory. When Reset is at  $V_{IL}$ , the memory is in reset mode: the outputs are high impedance and the current consumption is reduced to the Reset Supply Current  $I_{DD2}$ . Refer to *Table 21: DC characteristics - currents*, for the value of  $I_{DD2}$ . After Reset all blocks are in the Locked state and the Configuration Register is reset. When Reset is at  $V_{IH}$ , the device is in normal operation. Exiting reset mode the device enters asynchronous read mode, but a negative transition of Chip Enable or Latch Enable is required to ensure valid data outputs.

The Reset pin can be interfaced with 3 V logic without any additional circuitry. It can be tied to V<sub>RPH</sub> (refer to *Table 22: DC characteristics - voltages*).

### 2.8 Latch Enable $(\overline{L})$

Latch Enable latches the ADQ0-ADQ15 and A16-A22 address bits on its rising edge. The address latch is transparent when Latch Enable is at  $V_{\rm IL}$  and it is inhibited when Latch Enable is at  $V_{\rm IH}$ .

#### 2.9 Clock (K)

The clock input synchronizes the memory to the microcontroller during synchronous read operations; the address is latched on a Clock edge (rising or falling, according to the configuration settings) when Latch Enable is at  $V_{IL}$ . Clock is ignored during asynchronous read and in write operations.

### 2.10 **Wait (WAIT)**

Wait is an output signal used during synchronous read to indicate whether the data on the output bus are valid. This output is high impedance when Chip Enable is at  $V_{IH}$  or Reset is at  $V_{IL}$ . It can be configured to be active during the wait cycle or one clock cycle in advance. The WAIT signal is forced deasserted when Output Enable is at  $V_{IH}$ .

## 2.11 V<sub>DD</sub> supply voltage

V<sub>DD</sub> provides the power supply to the internal core of the memory device. It is the main power supply for all operations (Read, Program and Erase).

### 2.12 V<sub>DDQ</sub> supply voltage

$V_{DDQ}$  provides the power supply to the I/O pins and enables all Outputs to be powered independently from  $V_{DD}$ .  $V_{DDQ}$  can be tied to  $V_{DD}$  or can use a separate supply.

### 2.13 V<sub>PP</sub> Program supply voltage

$V_{\text{PP}}$  is both a control input and a power supply pin. The two functions are selected by the voltage range applied to the pin.

If  $V_{PP}$  is kept in a low voltage range (0V to  $V_{DDQ}$ )  $V_{PP}$  is seen as a control input. In this case a voltage lower than  $V_{PPLK}$  gives absolute protection against program or erase, while  $V_{PP}$  in the  $V_{PP1}$  range enables these functions (see Tables 21 and 22, DC Characteristics for the relevant values).  $V_{PP}$  is only sampled at the beginning of a program or erase; a change in its value after the operation has started does not have any effect and program or erase operations continue.

If  $V_{PP}$  is in the range of  $V_{PPH}$  it acts as a power supply pin. In this condition  $V_{PP}$  must be stable until the Program/Erase algorithm is completed.

### 2.14 V<sub>SS</sub> ground

V<sub>SS</sub> ground is the reference for the core supply. It must be connected to the system ground.

#### 2.15 V<sub>SSQ</sub> ground

$V_{SSQ}$  ground is the reference for the input/output circuitry driven by  $V_{DDQ}$ .  $V_{SSQ}$  must be connected to  $V_{SS}$

Note:

Each device in a system should have  $V_{DD}$ ,  $V_{DDQ}$  and  $V_{PP}$  decoupled with a 0.1  $\mu$ F ceramic capacitor close to the pin (high frequency, inherently low inductance capacitors should be as close as possible to the package). See Figure 8: AC measurement load circuit. The PCB track widths should be sufficient to carry the required  $V_{PP}$  program and erase currents.

### 3 Bus operations

There are six standard bus operations that control the device. These are Bus Read, Bus Write, Address Latch, Output Disable, Standby and Reset. See *Table 3: Bus operations*, for a summary.

Typically glitches of less than 5ns on Chip Enable or Write Enable are ignored by the memory and do not affect Bus Write operations.

#### 3.1 Bus Read

Bus Read operations are used to output the contents of the Memory Array, the Electronic Signature, the Status Register and the Common Flash Interface. Both Chip Enable and Output Enable must be at  $V_{\rm IL}$  in order to perform a read operation. The Chip Enable input should be used to enable the device. Output Enable should be used to gate data onto the output. The data read depends on the previous command written to the memory (see Command Interface section). See Figures 9, 10 and 11 Read AC Waveforms, and Tables 23 and 24 Read AC Characteristics, for details of when the output becomes valid.

#### 3.2 Bus Write

Bus Write operations write Commands to the memory or latch Input Data to be programmed. A bus write operation is initiated when Chip Enable and Write Enable are at  $V_{IL}$  with Output Enable at  $V_{IH}$ . Commands, Input Data and Addresses are latched on the rising edge of Write Enable or Chip Enable, whichever occurs first. The addresses must be latched prior to the write operation by toggling Latch Enable (when Chip Enable is at  $V_{IL}$ ). The Latch Enable must be tied to  $V_{IH}$  during the bus write operation.

See Figures 14 and 15, Write AC Waveforms, and Tables 25 and 26, Write AC Characteristics, for details of the timing requirements.

#### 3.3 Address Latch

Address latch operations input valid addresses. Both Chip enable and Latch Enable must be at  $V_{\rm IL}$  during address latch operations. The addresses are latched on the rising edge of Latch Enable.

### 3.4 Output Disable

The outputs are high impedance when the Output Enable is at V<sub>IH</sub>.

### 3.5 Standby

Standby disables most of the internal circuitry allowing a substantial reduction of the current consumption. The memory is in standby when Chip Enable and Reset are at  $V_{IH}$ . The power consumption is reduced to the standby level  $I_{DD3}$  and the outputs are set to high impedance, independently from the Output Enable or Write Enable inputs. If Chip Enable switches to  $V_{IH}$  during a program or erase operation, the device enters Standby mode when finished.

#### 3.6 Reset

During Reset mode the memory is deselected and the outputs are high impedance. The memory is in Reset mode when Reset is at  $V_{IL}$ . The power consumption is reduced to the Reset level, independently from the Chip Enable, Output Enable or Write Enable inputs. If Reset is pulled to  $V_{SS}$  during a Program or Erase, this operation is aborted and the memory content is no longer valid.

Table 3. Bus operations<sup>(1)</sup>

| Operation      | Ē               | G               | W               | Ī               | RP              | WAIT <sup>(2)</sup> | ADQ15-ADQ0    |

|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------|---------------|

| Bus Read       | $V_{IL}$        | $V_{IL}$        | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> |                     | Data Output   |

| Bus Write      | V <sub>IL</sub> | V <sub>IH</sub> | $V_{IL}$        | V <sub>IH</sub> | V <sub>IH</sub> |                     | Data Input    |

| Address Latch  | V <sub>IL</sub> | V <sub>IH</sub> | Х               | V <sub>IL</sub> | V <sub>IH</sub> |                     | Address Input |

| Output Disable | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IH</sub> |                     | Hi-Z          |

| Standby        | V <sub>IH</sub> | Х               | Х               | Х               | V <sub>IH</sub> | Hi-Z                | Hi-Z          |

| Reset          | X               | Х               | Х               | Χ               | $V_{IL}$        | Hi-Z                | Hi-Z          |

<sup>1.</sup> X = Don't care.

<sup>2.</sup> WAIT signal polarity is configured using the Set Configuration Register command.

### 4 Command interface

All Bus Write operations to the memory are interpreted by the Command Interface. Commands consist of one or more sequential Bus Write operations. An internal Program/Erase Controller handles all timings and verifies the correct execution of the program and erase commands. The Program/Erase Controller provides a Status Register whose output may be read at any time to monitor the progress or the result of the operation.

The Command Interface is reset to read mode when power is first applied, when exiting from Reset or whenever  $V_{DD}$  is lower than  $V_{LKO}$ . Command sequences must be followed exactly. Any invalid combination of commands will be ignored.

Refer to *Table 4: Command codes*, *Table 5: Standard commands*, *Table 6: Factory Commands*, and *Appendix D: Command interface state tables*, for a summary of the Command Interface.

Table 4. Command codes

| Hex Code | Command                                                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------------------|

| 01h      | Block Lock Confirm                                                                                                         |

| 03h      | Set Configuration Register Confirm                                                                                         |

| 10h      | Alternative Program Setup                                                                                                  |

| 20h      | Block Erase Setup                                                                                                          |

| 2Fh      | Block Lock-Down Confirm                                                                                                    |

| 40h      | Program Setup                                                                                                              |

| 50h      | Clear Status Register                                                                                                      |

| 60h      | Block Lock Setup, Block Unlock Setup, Block Lock Down Setup and Set<br>Configuration Register Setup                        |

| 70h      | Read Status Register                                                                                                       |

| 80h      | Buffer Enhanced Factory Program Setup                                                                                      |

| 90h      | Read Electronic Signature                                                                                                  |

| 98h      | Read CFI Query                                                                                                             |

| B0h      | Program/Erase Suspend                                                                                                      |

| BCh      | Blank Check Setup                                                                                                          |

| C0h      | Protection Register Program                                                                                                |

| CBh      | Blank Check Confirm                                                                                                        |

| D0h      | Program/Erase Resume, Block Erase Confirm, Block Unlock Confirm, Buffer Program or Buffer Enhanced Factory Program Confirm |

| E8h      | Buffer Program                                                                                                             |

| FFh      | Read Array                                                                                                                 |

#### 4.1 Read Array command

The Read Array command returns the addressed bank to Read Array mode.

One Bus Write cycle is required to issue the Read Array command. Once a bank is in Read Array mode, subsequent read operations will output the data from the memory array.

A Read Array command can be issued to any banks while programming or erasing in another bank.

If the Read Array command is issued to a bank currently executing a program or erase operation, the bank will return to Read Array mode but the program or erase operation will continue, however the data output from the bank is not guaranteed until the program or erase operation has finished. The read modes of other banks are not affected.

#### 4.2 Read Status Register command

The device contains a Status Register that is used to monitor program or erase operations.

The Read Status Register command is used to read the contents of the Status Register for the addressed bank.

One Bus Write cycle is required to issue the Read Status Register command. Once a bank is in Read Status Register mode, subsequent read operations will output the contents of the Status Register.

The Status Register data is latched on the falling edge of the Chip Enable or Output Enable signals. Either Chip Enable or Output Enable must be toggled to update the Status Register data

The Read Status Register command can be issued at any time, even during program or erase operations. The Read Status Register command will only change the read mode of the addressed bank. The read modes of other banks are not affected. Only Asynchronous Read and Single Synchronous Read operations should be used to read the Status Register. A Read Array command is required to return the bank to Read Array mode.

See Table 9 for the description of the Status Register Bits.

#### 4.3 Read Electronic Signature command

The Read Electronic Signature command is used to read the Manufacturer and Device Codes, the Lock Status of the addressed bank, the Protection Register, and the Configuration Register.

One Bus Write cycle is required to issue the Read Electronic Signature command. Once a bank is in Read Electronic Signature mode, subsequent read operations in the same bank will output the Manufacturer Code, the Device Code, the Lock Status of the addressed bank, the Protection Register, or the Configuration Register (see *Table 7*).

The Read Electronic Signature command can be issued at any time, even during program or erase operations, except during Protection Register Program operations. Dual operations between the Parameter bank and the Electronic Signature location are not allowed (see *Table 15: Dual operation limitations* for details).

If a Read Electronic Signature command is issued to a bank that is executing a program or erase operation the bank will go into Read Electronic Signature mode. Subsequent Bus Read cycles will output the Electronic Signature data and the Program/Erase controller will continue to program or erase in the background.

The Read Electronic Signature command will only change the read mode of the addressed bank. The read modes of other banks are not affected. Only Asynchronous Read and Single Synchronous Read operations should be used to read the Electronic Signature. A Read Array command is required to return the bank to Read Array mode.

#### 4.4 Read CFI Query command

The Read CFI Query command is used to read data from the Common Flash Interface (CFI).

One Bus Write cycle is required to issue the Read CFI Query command. Once a bank is in Read CFI Query mode, subsequent Bus Read operations in the same bank read from the Common Flash Interface.

The Read CFI Query command can be issued at any time, even during program or erase operations.

If a Read CFI Query command is issued to a bank that is executing a program or erase operation the bank will go into Read CFI Query mode. Subsequent Bus Read cycles will output the CFI data and the Program/Erase controller will continue to program or erase in the background.

The Read CFI Query command will only change the read mode of the addressed bank. The read modes of other banks are not affected. Only Asynchronous Read and Single Synchronous Read operations should be used to read from the CFI. A Read Array command is required to return the bank to Read Array mode. Dual operations between the Parameter Bank and the CFI memory space are not allowed (see *Table 15: Dual operation limitations* for details).

See *Appendix B: Common Flash Interface*, Tables *32*, *33*, *34*, *35*, *36*, *37*, *38*, *39*, *40* and *41* for details on the information contained in the Common Flash Interface memory area.

#### 4.5 Clear Status Register command

The Clear Status Register command can be used to reset (set to '0') all error bits (SR1, 3, 4 and 5) in the Status Register.

One Bus Write cycle is required to issue the Clear Status Register command. The Clear Status Register command does not affect the read mode of the bank.

The error bits in the Status Register do not automatically return to '0' when a new command is issued. The error bits in the Status Register should be cleared before attempting a new program or erase command.

#### 4.6 Block Erase command

The Block Erase command is used to erase a block. It sets all the bits within the selected block to '1'. All previous data in the block is lost.

If the block is protected then the erase operation will abort, the data in the block will not be changed and the Status Register will output the error.

Two Bus Write cycles are required to issue the command.

- The first bus cycle sets up the Block Erase command.

- The second latches the block address and starts the Program/Erase Controller.

If the second bus cycle is not the Block Erase Confirm code, Status Register bits SR4 and SR5 are set and the command is aborted.

Once the command is issued the bank enters Read Status Register mode and any read operation within the addressed bank will output the contents of the Status Register. A Read Array command is required to return the bank to Read Array mode.

During Block Erase operations the bank containing the block being erased will only accept the Read Array, Read Status Register, Read Electronic Signature, Read CFI Query and the Program/Erase Suspend command, all other commands will be ignored.

The Block Erase operation aborts if Reset,  $\overline{RP}$ , goes to  $V_{IL}$ . As data integrity cannot be guaranteed when the Block Erase operation is aborted, the block must be erased again.

Refer to Dual Operations section for detailed information about simultaneous operations allowed in banks not being erased.

Typical Erase times are given in Table 17: Program/Erase times and endurance cycles.

See *Appendix C*, *Figure 24: Block Erase flowchart and pseudo code*, for a suggested flowchart for using the Block Erase command.

#### 4.7 The Blank Check command

The Blank Check command is used to check whether a Main Array Block has been completely erased. Only one Block at a time can be checked. To use the Blank Check command V<sub>PP</sub> must be equal to V<sub>PPH</sub>. If V<sub>PP</sub> is not equal to V<sub>PPH</sub>, the device ignores the command and no error is shown in the Status Register.

Two bus cycles are required to issue the Blank Check command:

- The first bus cycle writes the Blank Check command (BCh) to any address in the Block to be checked.

- The second bus cycle writes the Blank Check Confirm command (CBh) to any address in the Block to be checked and starts the Blank Check operation.

If the second bus cycle is not Blank Check Confirm, Status Register bits SR4 and SR5 are set to '1' and the command aborts.

Once the command is issued the addressed bank automatically enters the Status Register mode and further reads within the bank output the Status Register contents.

The only operation permitted during Blank Check is Read Status Register. Dual Operations are not supported while a Blank Check operation is in progress. Blank Check operations cannot be suspended and are not allowed while the device is in Program/Erase Suspend.

The SR7 Status Register bit indicates the status of the Blank Check operation in progress: SR7 = '0' means that the Blank Check operation is still ongoing. SR7 = '1' means that the operation is complete.

The SR5 Status Register bit goes High (SR5 = '1') to indicate that the Blank Check operation has failed.

At the end of the operation the bank remains in the Read Status Register mode until another command is written to the Command Interface.

See Appendix C, Figure 21: Blank Check flowchart and pseudo code, for a suggested flowchart for using the Blank Check command.

Typical Blank Check times are given in Table 17: Program/Erase times and endurance cycles.

#### 4.8 Program command

The program command is used to program a single Word to the memory array.

If the block being programmed is protected, then the Program operation will abort, the data in the block will not be changed and the Status Register will output the error.

Two Bus Write cycles are required to issue the Program Command.

- The first bus cycle sets up the Program command.

- The second latches the address and data to be programmed and starts the Program/Erase Controller.

Once the programming has started, read operations in the bank being programmed output the Status Register content.

During a Program operation, the bank containing the Word being programmed will only accept the Read Array, Read Status Register, Read Electronic Signature, Read CFI Query and the Program/Erase Suspend command, all other commands will be ignored. A Read Array command is required to return the bank to Read Array mode.

Refer to Dual Operations section for detailed information about simultaneous operations allowed in banks not being programmed.

Typical Program times are given in Table 17: Program/Erase times and endurance cycles.

The Program operation aborts if Reset,  $\overline{RP}$ , goes to  $V_{IL}$ . As data integrity cannot be guaranteed when the Program operation is aborted, the Word must be reprogrammed.

See *Appendix C*, *Figure 20: Program flowchart and pseudo code*, for the flowchart for using the Program command.

#### 4.9 Buffer Program command

The Buffer Program Command makes use of the device's 32-Word Write Buffer to speed up programming. Up to 32 Words can be loaded into the Write Buffer. The Buffer Program command dramatically reduces in-system programming time compared to the standard non-buffered Program command.

Four successive steps are required to issue the Buffer Program command.

1. The first Bus Write cycle sets up the Buffer Program command. The setup code can be addressed to any location within the targeted block.

After the first Bus Write cycle, read operations in the bank will output the contents of the Status Register. Status Register bit SR7 should be read to check that the buffer is available (SR7 = 1). If the buffer is not available (SR7 = 0), re-issue the Buffer Program command to update the Status Register contents.

- The second Bus Write cycle sets up the number of Words to be programmed. Value n

is written to the same block address, where n+1 is the number of Words to be

programmed.

- 3. Use n+1 Bus Write cycles to load the address and data for each Word into the Write Buffer. Addresses must lie within the range from the start address to the start address + n, where the start address is the location of the first data to be programmed. Optimum performance is obtained when the start address corresponds to a 32 Word boundary.

- 4. The final Bus Write cycle confirms the Buffer Program command and starts the program operation.

All the addresses used in the Buffer Program operation must lie within the same block.

Invalid address combinations or failing to follow the correct sequence of Bus Write cycles will set an error in the Status Register and abort the operation without affecting the data in the memory array.

If the Status Register bits SR4 and SR5 are set to '1', the Buffer Program Command is not accepted. Clear the Status Register before re-issuing the command.

If the block being programmed is protected an error will be set in the Status Register and the operation will abort without affecting the data in the memory array.

During Buffer Program operations the bank being programmed will only accept the Read Array, Read Status Register, Read Electronic Signature, Read CFI Query and the Program/Erase Suspend command, all other commands will be ignored.

Refer to Dual Operations section for detailed information about simultaneous operations allowed in banks not being programmed.

See *Appendix C*, *Figure 22: Buffer Program flowchart and pseudo code*, for a suggested flowchart on using the Buffer Program command.

#### 4.10 Buffer Enhanced Factory Program command

The Buffer Enhanced Factory Program command has been specially developed to speed up programming in manufacturing environments where the programming time is critical.

It is used to program one or more Write Buffer(s) of 32 Words to a block. Once the device enters Buffer Enhanced Factory Program mode, the Write Buffer can be reloaded any number of times as long as the address remains within the same block. Only one block can be programmed at a time.

If the block being programmed is protected, then the Program operation will abort, the data in the block will not be changed and the Status Register will output the error.

The use of the Buffer Enhanced Factory Program command requires certain operating conditions:

- V<sub>PP</sub> must be set to V<sub>PPH</sub>

- V<sub>DD</sub> must be within operating range

- Ambient temperature T<sub>A</sub> must be 30°C ± 10°C

- The targeted block must be unlocked

- The start address must be aligned with the start of a 32 Word buffer boundary

- The address must remain the Start Address throughout programming.

Dual operations are not supported during the Buffer Enhanced Factory Program operation and the command cannot be suspended.

The Buffer Enhanced Factory Program Command consists of three phases: the Setup Phase, the Program and Verify Phase, and the Exit Phase, Please refer to *Table 6: Factory Commands* for detail information.

#### 4.10.1 Setup Phase

The Buffer Enhanced Factory Program command requires two Bus Write cycles to initiate the command.

- The first Bus Write cycle sets up the Buffer Enhanced Factory Program command.

- The second Bus Write cycle confirms the command.

After the confirm command is issued, read operations output the contents of the Status Register. The read Status Register command must not be issued as it will be interpreted as data to program.

The Status Register P/E.C. Bit SR7 should be read to check that the P/E.C. is ready to proceed to the next phase.

If an error is detected, SR4 goes high (set to '1') and the Buffer Enhanced Factory Program operation is terminated. See Status Register section for details on the error.

#### 4.10.2 Program and Verify Phase

The Program and Verify Phase requires 32 cycles to program the 32 Words to the Write Buffer. The data is stored sequentially, starting at the first address of the Write Buffer, until the Write Buffer is full (32 Words). To program less than 32 Words, the remaining Words should be programmed with FFFFh.

Three successive steps are required to issue and execute the Program and Verify Phase of the command.

- Use one Bus Write operation to latch the Start Address and the first Word to be programmed. The Status Register Bank Write Status bit SR0 should be read to check that the P/E.C. is ready for the next Word.

- 2. Each subsequent Word to be programmed is latched with a new Bus Write operation. The address must remain the Start Address as the P/E.C. increments the address location. If any address that is not in the same block as the Start Address is given, the Program and Verify Phase terminates. Status Register bit SR0 should be read between each Bus Write cycle to check that the P/E.C. is ready for the next Word.

- Once the Write Buffer is full, the data is programmed sequentially to the memory array.

After the program operation the device automatically verifies the data and reprograms if necessary.

The Program and Verify phase can be repeated, without re-issuing the command, to program additional 32 Word locations as long as the address remains in the same block.

4. Finally, after all Words, or the entire block have been programmed, write one Bus Write operation to any address outside the block containing the Start Address, to terminate Program and Verify Phase.

Status Register bit SR0 must be checked to determine whether the program operation is finished. The Status Register may be checked for errors at any time but it must be checked after the entire block has been programmed.

#### 4.10.3 Exit Phase

Status Register P/E.C. bit SR7 set to '1' indicates that the device has exited the Buffer Enhanced Factory Program operation and returned to Read Status Register mode. A full Status Register check should be done to ensure that the block has been successfully programmed. See the section on the Status Register for more details.

For optimum performance the Buffer Enhanced Factory Program command should be limited to a maximum of 100 program/erase cycles per block. If this limit is exceeded the internal algorithm will continue to work properly but some degradation in performance is possible. Typical program times are given in *Table 17*.

See Appendix C, Figure 28: Buffer Enhanced Factory Program flowchart and pseudo code, for a suggested flowchart on using the Buffer Enhanced Factory Program command.

#### 4.11 Program/Erase Suspend command

The Program/Erase Suspend command is used to pause a Program or Block Erase operation. The command can be addressed to any bank.

The Program/Erase Resume command is required to restart the suspended operation.

One bus write cycle is required to issue the Program/Erase Suspend command. Once the Program/Erase Controller has paused bits SR7, SR6 and/ or SR2 of the Status Register will be set to '1'.

The following commands are accepted during Program/Erase Suspend:

- Program/Erase Resume

- Read Array (data from erase-suspended block or program-suspended Word is not valid)

- Read Status Register

- Read Electronic Signature

- Read CFI Query.

Additionally, if the suspended operation was a Block Erase then the following commands are also accepted:

- Clear Status Register

- Set Configuration Register

- Program (except in erase-suspended block)

- Buffer Program (except in erase suspended blocks)

- Block Lock

- Block Lock-Down

- Block Unlock.

During an erase suspend the block being erased can be protected by issuing the Block Lock or Block Lock-Down commands. When the Program/Erase Resume command is issued the operation will complete.

It is possible to accumulate multiple suspend operations. For example: suspend an erase operation, start a program operation, suspend the program operation, then read the array.

If a Program command is issued during a Block Erase Suspend, the erase operation cannot be resumed until the program operation has completed.

The Program/Erase Suspend command does not change the read mode of the banks. If the suspended bank was in Read Status Register, Read Electronic signature or Read CFI Query mode the bank remains in that mode and outputs the corresponding data.

Refer to Dual Operations section for detailed information about simultaneous operations allowed during Program/Erase Suspend.

During a Program/Erase Suspend, the device can be placed in standby mode by taking Chip Enable to  $V_{IH}$ . Program/erase is aborted if Reset,  $\overline{RP}$ , goes to  $V_{II}$ .

See Appendix C, Figure 23: Program Suspend & Resume flowchart and pseudo code, and Figure 25: Erase Suspend & Resume flowchart and pseudo code, for flowcharts for using the Program/Erase Suspend command.

#### 4.12 Program/Erase Resume command

The Program/Erase Resume command is used to restart the program or erase operation suspended by the Program/Erase Suspend command. One Bus Write cycle is required to issue the command. The command can be issued to any address.

The Program/Erase Resume command does not change the read mode of the banks. If the suspended bank was in Read Status Register, Read Electronic signature or Read CFI Query mode the bank remains in that mode and outputs the corresponding data.

If a Program command is issued during a Block Erase Suspend, then the erase cannot be resumed until the program operation has completed.

See Appendix C, Figure 23: Program Suspend & Resume flowchart and pseudo code, and Figure 25: Erase Suspend & Resume flowchart and pseudo code, for flowcharts for using the Program/Erase Resume command.

#### 4.13 Protection Register Program command

The Protection Register Program command is used to program the user One-Time-Programmable (OTP) segments of the Protection Register and the two Protection Register Locks.

The device features 16 OTP segments of 128 bits and one OTP segment of 64 bits, as shown in *Figure 4: Protection Register memory map*.

The segments are programmed one Word at a time. When shipped all bits in the segment are set to '1'. The user can only program the bits to '0'.

Two Bus Write cycles are required to issue the Protection Register Program command.

- The first bus cycle sets up the Protection Register Program command.

- The second latches the address and data to be programmed to the Protection Register and starts the Program/Erase Controller.

Read operations to the bank being programmed output the Status Register content after the program operation has started.

Attempting to program a previously protected Protection Register will result in a Status Register error.

The Protection Register Program cannot be suspended. Dual operations between the Parameter Bank and the Protection Register memory space are not allowed (see *Table 15: Dual operation limitations* for details)

The two Protection Register Locks are used to protect the OTP segments from further modification. The protection of the OTP segments is not reversible. Refer to *Figure 4: Protection Register memory map*, and *Table 8: Protection Register locks*, for details on the Lock bits.

See Appendix C, Figure 27: Protection Register Program flowchart and pseudo code, for a flowchart for using the Protection Register Program command.

#### 4.14 Set Configuration Register command

The Set Configuration Register command is used to write a new value to the Configuration Register.

Two Bus Write cycles are required to issue the Set Configuration Register command.

- The first cycle sets up the Set Configuration Register command and the address corresponding to the Configuration Register content.

- The second cycle writes the Configuration Register data and the confirm command.

The Configuration Register data must be written as an address during the bus write cycles, that is ADQ0 = CR0, ADQ1 = CR1, ..., ADQ15 = CR15. Addresses A16-Amax are ignored.

Read operations output the array content after the Set Configuration Register command is issued.

The Read Electronic Signature command is required to read the updated contents of the Configuration Register.

#### 4.15 Block Lock command

The Block Lock command is used to lock a block and prevent program or erase operations from changing the data in it. All blocks are locked after power-up or reset.

Two Bus Write cycles are required to issue the Block Lock command.

- The first bus cycle sets up the Block Lock command.

- The second Bus Write cycle latches the block address and locks the block.

The lock status can be monitored for each block using the Read Electronic Signature command. *Table 16* shows the Lock Status after issuing a Block Lock command.

Once set, the Block Lock bits remain set even after a hardware reset or power-down/power-up. They are cleared by a Block Unlock command.

Refer to the section, Block Locking, for a detailed explanation. See *Appendix C*, *Figure 26: Locking operations flowchart and pseudo code*, for a flowchart for using the Lock command.

#### 4.16 Block Unlock command

The Block Unlock command is used to unlock a block, allowing the block to be programmed or erased.

Two Bus Write cycles are required to issue the Block Unlock command.

- The first bus cycle sets up the Block Unlock command.

- The second Bus Write cycle latches the block address and unlocks the block.

The lock status can be monitored for each block using the Read Electronic Signature command. *Table 16* shows the protection status after issuing a Block Unlock command.

Refer to the section, Block Locking, for a detailed explanation and *Appendix C*, *Figure 26: Locking operations flowchart and pseudo code*, for a flowchart for using the Block Unlock command.

#### 4.17 **Block Lock-Down command**

The Block Lock-Down command is used to lock-down a locked or unlocked block.

A locked-down block cannot be programmed or erased. The lock status of a locked-down block cannot be changed when  $\overline{WP}$  is low,  $V_{IL}$ . When  $\overline{WP}$  is high,  $V_{IH}$ , the lock-down function is disabled and the locked blocks can be individually unlocked by the Block Unlock command.

Two Bus Write cycles are required to issue the Block Lock-Down command.

- The first bus cycle sets up the Block Lock-Down command.

- The second Bus Write cycle latches the block address and locks-down the block.

The lock status can be monitored for each block using the Read Electronic Signature command.

Locked-Down blocks revert to the locked (and not locked-down) state when the device is reset on power-down. Table 16 shows the Lock Status after issuing a Block Lock-Down command.

Refer to the section, Block Locking, for a detailed explanation and Appendix C, Figure 26: Locking operations flowchart and pseudo code, for a flowchart for using the Lock-Down command.

Table 5. Standard commands<sup>(1)</sup>

|                               |        | Bus operations |                                |                   |           |                    |                 |  |  |  |  |

|-------------------------------|--------|----------------|--------------------------------|-------------------|-----------|--------------------|-----------------|--|--|--|--|

| Commands                      | Cycles |                | 1st cycle                      |                   | 2nd cycle |                    |                 |  |  |  |  |

|                               | ၁      | Op.            | Add                            | Data              | Op.       | Add                | Data            |  |  |  |  |

| Read Array                    | 1+     | Write          | BKA                            | FFh               | Read      | WA                 | RD              |  |  |  |  |

| Read Status Register          | 1+     | Write          | BKA                            | 70h               | Read      | BKA <sup>(2)</sup> | SRD             |  |  |  |  |

| Read Electronic Signature     | 1+     | Write          | BKA                            | 90h               | Read      | BKA <sup>(2)</sup> | ESD             |  |  |  |  |

| Read CFI Query                | 1+     | Write          | BKA                            | 98h               | Read      | BKA <sup>(2)</sup> | QD              |  |  |  |  |

| Clear Status Register         | 1      | Write          | Х                              | 50h               |           |                    |                 |  |  |  |  |

| Block Erase                   | 2      | Write          | BKA or<br>BA <sup>(3)</sup>    | 20h               | Write     | ВА                 | D0h             |  |  |  |  |

| Program                       | 2      | Write          | BKA or<br>WA <sup>(3)</sup>    | 40h or<br>10h     | Write     | WA                 | PD              |  |  |  |  |

|                               |        | Write          | BA                             | E8h               | Write     | BA                 | n               |  |  |  |  |

| Buffer Program <sup>(4)</sup> | n+4    | Write          | PA <sub>1</sub>                | PD <sub>1</sub>   | Write     | PA <sub>2</sub>    | PD <sub>2</sub> |  |  |  |  |

|                               |        | Write          | PA <sub>n+1</sub>              | PD <sub>n+1</sub> | Write     | Х                  | D0h             |  |  |  |  |

| Program/Erase Suspend         | 1      | Write          | Х                              | B0h               |           |                    |                 |  |  |  |  |

| Program/Erase Resume          | 1      | Write          | Х                              | D0h               |           |                    |                 |  |  |  |  |

| Protection Register Program   | 2      | Write          | PRA                            | C0h               | Write     | PRA                | PRD             |  |  |  |  |

| Set Configuration Register    | 2      | Write          | CRD                            | 60h               | Write     | CRD                | 03h             |  |  |  |  |

| Block Lock                    | 2      | Write          | Write BKA or BA <sup>(3)</sup> |                   | Write     | ВА                 | 01h             |  |  |  |  |

| Block Unlock                  | 2      | Write          | BKA or<br>BA <sup>(3)</sup>    | 60h               | Write     | ВА                 | D0h             |  |  |  |  |

| Block Lock-Down               | 2      | Write          | BKA or<br>BA <sup>(3)</sup>    | 60h               | Write     | ВА                 | 2Fh             |  |  |  |  |

X = Don't Care, WA = Word Address in targeted bank, RD = Read Data, SRD = Status Register Data, ESD = Electronic Signature Data, QD = Query Data, BA = Block Address, BKA = Bank Address, PD = Program Data, PRA = Protection Register Address, PRD = Protection Register Data, CRD = Configuration Register Data.

<sup>2.</sup> Must be same bank as in the first cycle. The signature addresses are listed in *Table 7*.

<sup>3.</sup> Any address within the bank can be used.

<sup>4.</sup> n+1 is the number of Words to be programmed.

Table 6. Factory Commands

|                                          |                                   | · uotor, oommunuo |                                       |                                     |                 |                 |                 |                 |     |                 |                  |                 |                  |  |

|------------------------------------------|-----------------------------------|-------------------|---------------------------------------|-------------------------------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|------------------|-----------------|------------------|--|

|                                          | Phase                             | (0                |                                       | Bus Write operations <sup>(1)</sup> |                 |                 |                 |                 |     |                 |                  |                 |                  |  |

| Command                                  |                                   | Phase             | Cycles                                | 1s                                  | t               | 2r              | 2nd             |                 | 3rd |                 | Final -1         |                 | Final            |  |

|                                          |                                   | 0                 | Add                                   | Data                                | Add             | Data            | Add             | Data            |     | Add             | Data             | Add             | Data             |  |

| Blank<br>Check                           |                                   | 2                 | ВА                                    | BCh                                 | ВА              | CBh             |                 |                 |     |                 |                  |                 |                  |  |

| Buffer<br>Enhanced<br>Factory<br>Program | Setup                             | 2                 | BKA or<br>WA <sup>(2)</sup>           | 80h                                 | WA <sub>1</sub> | D0h             |                 |                 |     |                 |                  |                 |                  |  |

|                                          | Program/<br>Verify <sup>(3)</sup> | ≥32               | WA <sub>1</sub>                       | PD <sub>1</sub>                     | WA <sub>1</sub> | PD <sub>2</sub> | WA <sub>1</sub> | PD <sub>3</sub> |     | WA <sub>1</sub> | PD <sub>31</sub> | WA <sub>1</sub> | PD <sub>32</sub> |  |

|                                          | Exit                              | 1                 | NOT<br>BA <sub>1</sub> <sup>(4)</sup> | Х                                   |                 |                 |                 |                 |     |                 |                  |                 |                  |  |

- WA = Word Address in targeted bank, BKA = Bank Address, PD = Program Data, BA = Block Address, X = Don't Care.

- 2. Any address within the bank can be used.

- 3. The Program/Verify phase can be executed any number of times as long as the data is to be programmed to the same block.

- 4.  $WA_1$  is the Start Address, NOT  $BA_1$  = Not Block Address of  $WA_1$ .

Table 7. Electronic signature codes

|                                 | Code                        | Address (h)                             | Data (h)             |

|---------------------------------|-----------------------------|-----------------------------------------|----------------------|

| Manufacturer Code               |                             | Bank Address + 00                       | 0020                 |

| Device Code                     | Тор                         | Bank Address + 01                       | 882E (M58LR128HC)    |

|                                 | Bottom                      | Bank Address + 01                       | 882F (M58LR128HD)    |

| Block Protection                | Locked                      |                                         | 0001                 |

|                                 | Unlocked                    | Block Address + 02                      | 0000                 |

|                                 | Locked and Locked-Down      |                                         | 0003                 |

|                                 | Unlocked and Locked-Down    |                                         | 0002                 |

| Die Revision Code               |                             | Bank Address + 03                       | DRC <sup>(1)</sup>   |

| Configuration Register          |                             | Bank Address + 05                       | CR <sup>(1)</sup>    |

| Protection Register<br>PR0 Lock | Numonyx Factory Default     |                                         | 0002                 |

|                                 | OTP Area Permanently Locked | Bank Address + 80                       | 0000                 |

| Protection Pogister PE          | 20                          | Bank Address + 81<br>Bank Address + 84  | Unique Device Number |

| Protection Register PR0         |                             | Bank Address + 85<br>Bank Address + 88  | OTP Area             |

| Protection Register PF          | R1 through PR16 Lock        | Bank Address + 89                       | PRLD <sup>(1)</sup>  |

| Protection Registers P          | R1-PR16                     | Bank Address + 8A<br>Bank Address + 109 | OTP Area             |

<sup>1.</sup> CR = Configuration Register, PRLD = Protection Register Lock Data, DRC = Die Revision Code.

Figure 4. Protection Register memory map

**Protection Register locks** Table 8.

| Lock     |         |              | Description                                                              |  |

|----------|---------|--------------|--------------------------------------------------------------------------|--|

| Number   | Address | Bits         | Description                                                              |  |

| Lock 1 8 |         | Bit 0        | preprogrammed to protect Unique Device Number, address 81h to 84h in PR0 |  |

|          | 80h     | Bit 1        | protects 64bits of OTP segment, address 85h to 88h in PR0                |  |

|          |         | Bits 2 to 15 | reserved                                                                 |  |

| Lock 2   | 89h     | Bit 0        | protects 128bits of OTP segment PR1                                      |  |

|          |         | Bit 1        | protects 128bits of OTP segment PR2                                      |  |

|          |         | Bit 2        | protects 128bits of OTP segment PR3                                      |  |

|          |         |              |                                                                          |  |

|          |         | Bit 13       | protects 128bits of OTP segment PR14                                     |  |

|          |         | Bit 14       | protects 128bits of OTP segment PR15                                     |  |

|          |         | Bit 15       | protects 128bits of OTP segment PR16                                     |  |

### 5 Status Register

The Status Register provides information on the current or previous program or erase operations. Issue a Read Status Register command to read the contents of the Status Register, refer to Read Status Register Command section for more details. To output the contents, the Status Register is latched and updated on the falling edge of the Chip Enable or Output Enable signals and can be read until Chip Enable or Output Enable returns to  $V_{IH}$ . The Status Register can only be read using single Asynchronous or Single Synchronous reads. Bus Read operations from any address within the bank, always read the Status Register during program and erase operations.

The various bits convey information about the status and any errors of the operation. Bits SR7, SR6, SR2 and SR0 give information on the status of the device and are set and reset by the device. Bits SR5, SR4, SR3 and SR1 give information on errors, they are set by the device but must be reset by issuing a Clear Status Register command or a hardware reset. If an error bit is set to '1' the Status Register should be reset before issuing another command.

The bits in the Status Register are summarized in *Table 9: Status Register bits*. Refer to *Table 9* in conjunction with the following text descriptions.

### 5.1 Program/Erase Controller status bit (SR7)

The Program/Erase Controller Status bit indicates whether the Program/Erase Controller is active or inactive in any bank.

When the Program/Erase Controller Status bit is Low (set to '0'), the Program/Erase Controller is active; when the bit is High (set to '1'), the Program/Erase Controller is inactive, and the device is ready to process a new command.

The Program/Erase Controller Status bit is Low immediately after a Program/Erase Suspend command is issued until the Program/Erase Controller pauses. After the Program/Erase Controller pauses the bit is High.

### 5.2 Erase Suspend status bit (SR6)

The Erase Suspend Status bit indicates that an erase operation has been suspended in the addressed block. When the Erase Suspend Status bit is High (set to '1'), a Program/Erase Suspend command has been issued and the memory is waiting for a Program/Erase Resume command.

The Erase Suspend Status bit should only be considered valid when the Program/Erase Controller Status bit is High (Program/Erase Controller inactive). SR6 is set within the Erase Suspend Latency time of the Program/Erase Suspend command being issued therefore the memory may still complete the operation rather than entering the Suspend mode.

When a Program/Erase Resume command is issued the Erase Suspend Status bit returns Low.

#### 5.3 Erase/Blank Check status bit (SR5)

The Erase/Blank Check Status bit is used to identify if there was an error during a Block Erase operation. When the Erase/Blank Check Status bit is High (set to '1'), the Program/Erase Controller has applied the maximum number of pulses to the block and still failed to verify that it has erased correctly.

The Erase/Blank Check Status bit should be read once the Program/Erase Controller Status bit is High (Program/Erase Controller inactive).

The Erase/Blank Check Status bit is also used to indicate whether an error occurred during the Blank Check operation: if the data at one or more locations in the block where the Blank Check command has been issued is different from FFFFh, SR5 is set to '1'.

Once set High, the Erase/Blank Check Status bit must be set Low by a Clear Status Register command or a hardware reset before a new erase command is issued, otherwise the new command will appear to fail.

#### 5.4 Program status bit (SR4)

The Program Status bit is used to identify if there was an error during a program operation.

The Program Status bit should be read once the Program/Erase Controller Status bit is High (Program/Erase Controller inactive).